# Experimental Analysis of Gate Leakage Current for FinFET versus Negative Capacitance FinFET

Eunah Ko, Jaemin Shin, Hyungki Cho, Kihun Choe and Changhwan Shin

Department of Electrical and Computer Engineering, University of Seoul, 163 Seoulsiripdae-ro, Seoul 02504, Republic of Korea (e-mail: cshin@uos.ac.kr, Tel: +82-2-6490-2348, FAX: +82-2-6490-2314).

**Abstract:** Negative capacitance (NC) Field-effect-transistors (FETs) or NC Fin-shaped FET (NC FinFET) which utilizes the negative capacitance effect of ferroelectric material such as PZT or BTO has been suggested as a new candidate for ultra-low power steep switching devices for integrated circuits. The effect of NC on FinFET device has been demonstrated by using experiment and simulation method. However, the reliability issue still hinders the commercialization of NC FinFET device, and has to be experimentally studied. For this, this study suggests the gate leakage current of NC FinFET device which has minimum subthreshold slope of ~25 mV/decade.

Keywords: negative capacitance, FinFET, gate leakage current, steep switching device

# 1. Introduction

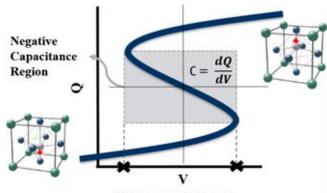

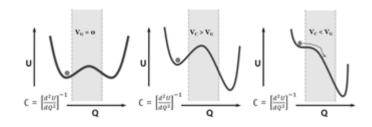

The need and importance of steep switching device (i.e., switching transistors with subthreshold slope (SS) value that is lower than 60 mV/decade, which is the limitation of SS value in conventional devices like MOSFET, FinFET because of the Boltzmann distribution of carriers) has been constantly highlighted for decades, to handle the exponential increase of power consumption in integrated circuits. There are candidates for steep switching device such as Tunnel Field-Effect-Transistor (TFET), Nanoelectromechanical Switch (NEMs), etc. Recent studies [1-13] demonstrated the steep switching characteristic of negative capacitance FETs that utilizes the polarization switching characteristic of ferroelectric material shown in Fig. 1, and Fig. 2. Fig. 1 plots the concept of negative capacitance. The polarization switching characteristic of ferroelectric material induces negative capacitance. The polarization comes from the nature of ferroelectric material, which has two minima point in energy curve shown in Fig. 2. When the external voltage V is lower than the coercive voltage, ferroelectric switching does not occur. However, when the external voltage is applied higher than coercive voltage, this induces polarization switching in ferroelectric material and therefore, the total system goes through the negative capacitance region shown in Fig. 1. In this situation, the capacitance value of ferroelectric capacitor is negative, and therefore, if the capacitor is connected in series with the conventional device such as FinFET, the SS value could be lowered more than 60 mV/decade (i.e., the m factor of SS 1+CS/Cins could be lower than 1 since Cins is negative). Indeed, the steep switching characteristic of NCFETs with ferroelectric capacitor, whether the ferroelectric layer is connected in series or it is integrated at the top of the device, has been experimentally demonstrated in recent 10 years. Furthermore, the critical method for lowering the hysteresis (which is the main problem in applying NCFET device in current CMOS logic) is also suggested and demonstrated. However, despite these findings, it is still questionable if the NCFET devices are reliable. That is to say, it should be clarified that the steep switching arises from the voltage amplification effect, not the injection of gate leakage current. Therefore, in this study, the steep switching characteristic of NCFinFET device is demonstrated and compared with conventional FinFET device with the gate leakage current comparison.

X Coercive Voltage Vc

Fig. 1: The concept of negative capacitance. The polarization switching inside the ferroelectric material induces negative capacitance.

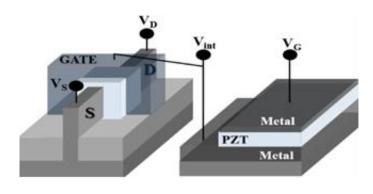

Fig. 3: Bird's eye view of negative capacitance FinFET device. The PZT ferroelectric capacitor is connected in series with the FinFET device by using metal wire.

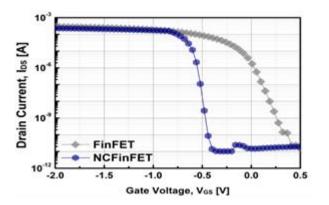

Fig. 5: Experimentally measured Drain current-Gate voltage characteristics of FinFET and NCFinFET device for forward sweep.

Fig. 2: The concept of coercive voltage of ferroelectric capacitor. The applied voltage should be higher than coercive voltage to induce polarization switching of ferroelectric material.

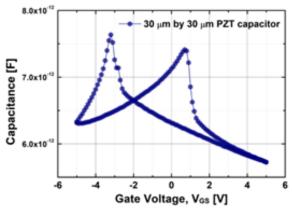

Fig. 4: Experimentally measured Charge-Voltage characteristic of fabricated PZT ferroelectric capacitor

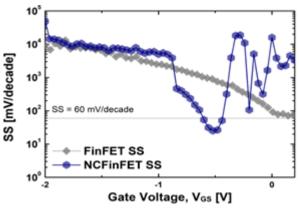

Fig. 6: Experimentally measured subthreshold slope-Gate voltage characteristics of FinFET and NCFinFET device for forward sweep.

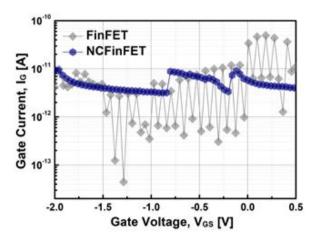

Fig. 7: Experimentally measured Gate current-Voltage characteristic of FinFET and NCFinFET.

## 2. Device Structure and Fabrication

### 2.1. Ferroelectric Capacitor

Typical ferroelectric material Pb(Zr<sub>0.2</sub>Ti<sub>0.8</sub>)O<sub>3</sub> (PZT) was deposited at the top of the bottom electrode of ferroelectric capacitor by pulsed laser deposition technique. The top metal contact size of PZT ferroelectric capacitor was 30  $\mu$ m × 30  $\mu$ m, and the thickness of PZT ferroelectric layer was 70 nm. The measured C-V characteristic of PZT ferroelectric capacitor is shown in Fig. 4.

#### 2.2. NCFinFET

To demonstrate the steep switching in state-of-the-art FinFET device, the FinFET with gate length of 45 nm, fin number of 5, fin width of 20 nm, fin height of 40 nm was prepared. To fabricate NCFinFET device, the bottom metal contact of PZT ferroelectric capacitor was connected in series with the gate metal contact of FinFET device by using gold wire. The gate voltage was applied to the top metal contact of PZT ferroelectric capacitor, and source/drain voltage was applied to the source/drain of FinFET device (see Fig. 3). The Keithley 4200A-SCS measurement equipment was used to experimentally measure the characteristics of devices.

## 3. Experimental Result and Discussion

Table I summarizes the performance parameters of FinFET and NCFinFET device shown in Fig. 5.

TABLE I: Performance Parameters of FinFET and NCFinFET

| Parameter [unit]               | FinFET                 | NCFinFET               |

|--------------------------------|------------------------|------------------------|

| Minimum SS [mV/decade]         | 65.07                  | 25.03                  |

| Average SS [mV/decade]         | 75.85                  | 31.13                  |

| $I_{ON}$ [A] @ $V_{GS} = -1$ V | $1.91 \times 10^{-4}$  | $1.73 \times 10^{-4}$  |

| $I_{OFF}$ [A] @ $V_{GS} = 0$ V | 3.40×10 <sup>-11</sup> | 5.79×10 <sup>-11</sup> |

Fig.5. Shows experimentally measured Drain current-Gate voltage characteristics of FinFET and NCFinFET device for forward sweep. Note that drain voltage was 0.5 V. It is clearly shown that the SS of NCFinFET device is much lower than that of FinFET device, because of the negative capacitance effect of PZT ferroelectric capacitor. The performance of FinFET and NCFinFET transfer curves are compared in Table I. To compare the SS characteristic clearly, the minimum SS (i.e., the minimum SS value measured as the SS between two measurement point) and average SS (i.e., the average SS which is calculated as the SS value for I<sub>DS</sub> of  $1\times10^{-10}$ ~ $1\times10^{-6}$ ) were measured. For both average and minimum SS values, SS of FinFET is ~ $2.5\times$  higher than that of NCFinFET. Furthermore, the on-state current (I<sub>ON</sub>) which is the drain current at V<sub>GS</sub> of -1 V and off-state current (I<sub>OFF</sub>) are similar between FinFET and NCFinFET. To compare the SS value for these two devices clearly, Fig. 6 plots experimentally measured subthreshold slope-Gate voltage characteristics of FinFET and NCFinFET device

for forward sweep. The SS of FinFET cannot overcome the limitation of 60 mV/decade, however, the SS of NCFinFET has about 5 points that overcomes this limitation. Fig. 7 plots the gate leakage current of FinFET and NCFinFET devices. Experimental result shows clearly that the gate leakage current of NCFinFET is similar to that of FinFET, thus, the steep switching characteristic of NCFinFET does not come from the gate leakage current since the value of gate leakage current is lower than  $\sim 10^{-11}$  A for V<sub>GS</sub> > 0 V.

## 4. Conclusion

Performance related to steep switching and device reliability of NC FinFET is experimentally demonstrated. Because of the negative capacitance effect, the subthreshold slope (both average and minimum subthreshold slope) is highly enhanced, compared to the baseline FinFET device only. For the reliability issue of NC FinFET device in terms of the gate leakage current, the gate leakage current of NC FinFET is experimentally demonstrated by using Keithley-4200A SCS equipment. We clearly demonstrated that the gate leakage current of NC FinFET is similar to that of FinFET device, thus, the steep switching characteristic of NC FinFET device does not originate from the leakage current.

# 5. Acknowledgment

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIP) (No. 2017R1A2A2A05069708). Also, this work was supported by the Future Semiconductor Device Technology Development Program (10067746) funded by the Ministry of Trade, Industry & Energy (MOTIE) and the Korea Semiconductor Research Consortium (KSRC).

## 6. References

- E. Ko, J. W. Lee, and C. Shin, "Negative Capacitance FinFET with Sub-20-mV/decade Subthreshold Slope and Minimal Hysteresis of 0.48 V," IEEE Electron Device Letters, vol. 38, no. 4, Apr. 2017, pp. 418-421.

- [2] E. Ko, H. Lee, Y. Goh, S. Jeon, and C. Shin, "Sub-60-mV/decade Negative Capacitance FinFET with Sub-10-nm Hafnium-Based Ferroelectric Capacitor," IEEE Journal of the Electron Devices Society, vol. 5, no. 5, Sep. 2017, pp. 306-309.

- [3] H. Lee, Y. Yoon, and C. Shin, "Current-voltage Model for Negative Capacitance field-Effect Transistors," IEEE Electron Device Letters, vol. 38, no. 5, May 2017, pp. 669-672.

- [4] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," Nano Letters, vol. 8, no. 12, Feb. 2008, pp. 405-410.

- [5] J. Jo and C. Shin, "Negative Capacitance Field Effect Transistor with Hysteresis-Free Sub-60-mV/decade Switching," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 245-248, Mar. 2016.

- [6] J. Jo and C. Shin, "Experimental observation of voltage amplification using negative capacitance for sub-60 mV/decade CMOS devices," *Current Appl. Phys.*, vol. 15, no. 3, pp. 352-355, Mar. 2015.

- [7] K. Majumdar, S. Datta, and S. P. Rao, "Revisiting the Theory of Ferroelectric Negative Capacitance," *IEEE Trans. Electron Devices*, vol. 63, no. 5, pp. 2043-2049, Mar. 2016.

- [8] J. Jo and C. Shin, "Impact of temperature on negative capacitance field-effect transistor," *IEEE Electronic Lett.*, vol. 51, no. 1, pp. 106-108, Jan. 2015.

- [9] J. Jo, W. Y. Choi, J.-D. Park, J. W. Shim, H.-Y. Yu, and C. Shin, "Negative Capacitance in Organic/Ferroelectric Capacitor to Implement Steep Switching MOS Devices," *Nano Lett.*, vol. 15, no. 7, pp. 4553-4556, Jun. 2015.

- [10] T. Tybell, C. H. Ahn, M. Foeth, and J. –M. Triscone, "Nanometer control of the ferroelectric polarization in Pb(Zr<sub>0.2</sub>Ti<sub>0.8</sub>)O<sub>3</sub> thin films," in *Proc. IEEE Int. Symp. Applications of Ferroelectrics*, Aug. 1998, pp. 431-434, DOI: <u>10.1109/ISAF.1998.786724</u>

- [11] A. I. Khan, U. Radhakrishna, K. Chatterjee, S. Salahuddin, and D. Antoniadis, "Negative Capacitance Behavior in a Leaky Ferroelectric," *IEEE Trans. Electron Devices*, vol. PP, no. 99, pp. 1-7, Oct. 2016, DOI: <u>10.1109/TED.2016.2612656</u>B

- [12] A. I. Khan, K. Chatterjee, J. P. Duarte, Z. Lu, A. Sachid, S. Khandelwal, R. Ramesh, C. Hu, and S. Salahuddin, "Negative Capacitance in Short-Channel FinFETs Externally Connected to an Epitaxial Ferroelectric Capacitor," *IEEE Electron Device Lett.*, vol. 37, no. 1, pp. 111-114, Jan. 2016, DOI: <u>10.1109/LED.2015.2501319</u>

- [13] A. I. Khan, X. Marti, C. Serrao, R. Ramesh, and S. Salahuddin, "Voltage-Controlled Ferroelectric Switching in Pb(Zr<sub>0.2</sub>Ti<sub>0.8</sub>)O<sub>3</sub> Thin Films," *Nano Lett.* 2015, 15, pp. 2229-2234, Mar. 2015, DOI: 10.1021/nl503806p.